- All templates

- Block diagrams templates

- Clock system block diagram

About this clock system block diagram

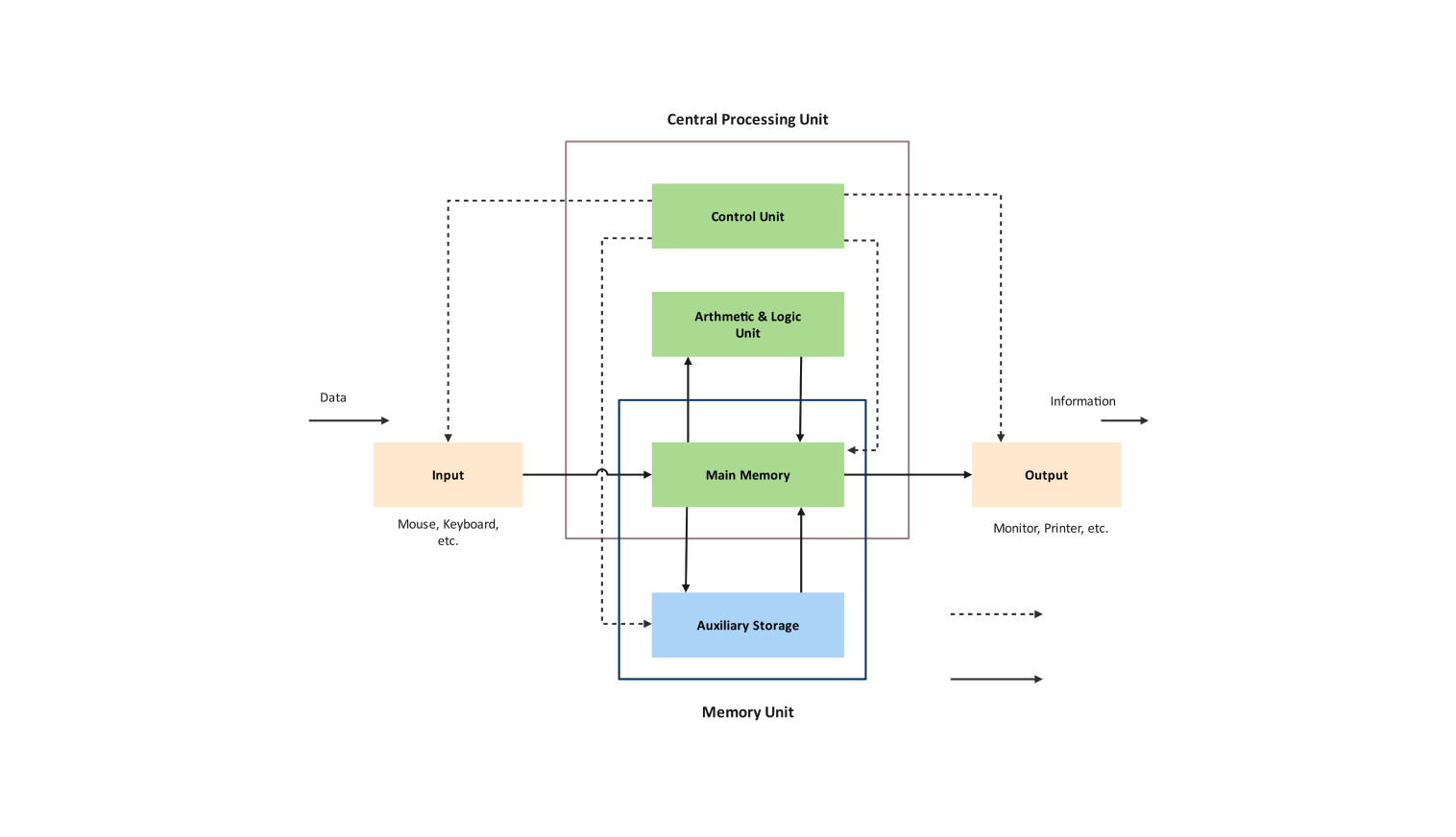

Clock system block diagrams are useful. They show the path of the timing signals that control the pace of a computing device's components. This diagram explains the detailed and complex wiring of the clock signals that affect the overall system speed and solidity.

The major clock switch and the major clock's prescaler are shown in the center of this block diagram of the clock system. These are important in the generation of base clock signals that are distributed in the system. The system uses a prescaler value to divide the clock frequency to appropriate levels.

Features for instance Non-Volatile Memory (NVM), Random Access Memory (RAM), and the Central Processing Unit (CPU) are illustrated as receiving the timing signals through the primary clock lines. This block diagram furthermore also includes devices that have time-sensitive peripherals to operate in the correct fashion which proves the fact that the clock system is indeed ubiquitous.

There are several sub-modules: the RTC, WDT, BOD, and TCD. They have specific connections to the clock system. Selector bars on these components show the flexibility of the clock source in the various performances depending on the system's needs.

All in all, this block diagram is an informative aid for systems designers and engineers. From a graphic point of view, it makes it easier to understand a computer system’s clocks.

Related templates

Get started with EdrawMax today

Create 210 types of diagrams online for free.

Draw a diagram free Draw a diagram free Draw a diagram free Draw a diagram free Draw a diagram free